XEMICS

# Data Book

# XX-XE88LC01/03/05

Ultra low-power mixed-signal microcontroller 300 uA at 1 MIPS 16 + 6 bits ADC

20001101

Copyright XEMICS

Printed in Switzerland

Date of release 03-00 03-00-0035 - Data book XX-XE88LC01-03-05

# **Table of contents**

|                        | Table       | e of contents                              | 3        |

|------------------------|-------------|--------------------------------------------|----------|

|                        | List        | of figures                                 | 9        |

|                        | List        | of tables                                  | 11       |

| 1                      | Intro       | duction                                    | 15       |

| 1.1                    |             | Conventions used in this document          | 15       |

| 2                      | VEO         |                                            | 17       |

| 2                      | XEð         | 000 MCU Family                             | 17       |

| 2.1                    |             | Features                                   | 17       |

| 2.2                    |             | Family                                     | 17       |

| 3                      | Powe        | er supply                                  | 19       |

| 3.1                    |             | In circuit power supply principle          | 19       |

| 3.2                    |             | Voltage regulator                          | 20       |

| 3.3                    |             | Voltage multiplier                         | 21       |

| 3.4                    |             | Current requirement                        | 22       |

| 4                      | Cent        | ral processing unit                        | 23       |

| 4.1                    | CCIII       | Introduction                               | 23       |

|                        | 1.1         | Pipeline                                   | 23       |

|                        | 1.1         | Gated clocks                               | 23       |

|                        | 1.2         | Low frequency modes                        | 25       |

|                        | 1.4         | Stand-by Mode                              | 26       |

|                        | 1.5         | CoolRISC <sup>©</sup> Core Features        | 26       |

| 4.2                    |             | Programmer's Model                         | 26       |

| 4.2                    | 2.1         | CoolRISC© 816 Architecture                 | 26       |

| 4.2                    | 2.2         | Instruction Set                            | 26       |

| 4.2                    | 2.3         | Register bank                              | 31       |

|                        | 2.4         | Program Memory addressing modes            | 32       |

|                        | 2.5         | Data Memory addressing modes               | 32       |

|                        | 2.6         | Flags Z, C & V                             | 36       |

|                        | 2.7         | ALU output register: a                     | 36       |

|                        | 2.8         | Program counter                            | 36       |

|                        | 2.9<br>2.10 | Branch conditions<br>Call, Branch and Link | 36<br>37 |

|                        | 2.10        | Events and Interrupts                      | 37       |

|                        | 2.12        | Pipeline exception                         | 39       |

|                        | 2.13        | HALT mode                                  | 39       |

|                        | 2.14        | Hardware Reset                             | 39       |

| 4.2                    | 2.15        | Low frequency modes                        | 39       |

| 5                      | Mem         | lory                                       | 41       |

| 5.1                    |             | Memory organisation                        | 41       |

| 5.2                    |             | Program memory                             | 41       |

| 5.3                    |             | Data memory                                | 41       |

| 5.4                    |             | Peripherals mapping                        | 42       |

| 5. <del>4</del><br>5.5 |             | Address pack                               | 42       |

| 5.5<br>5.6             |             | 1                                          | 42       |

| 5.0                    |             | MTP Flash memory programmation             | 42       |

| 5.6.1          | Introduction                                      | 42       |

|----------------|---------------------------------------------------|----------|

| 5.6.2          | MTP Registers                                     | 43       |

| 6 Sys          | stem operating modes                              | 45       |

| 6.1            | Operating modes                                   | 45       |

| 6.1.1          | Start-up and Reset states                         | 45       |

| 6.1.2          | Active mode                                       | 45       |

| 6.1.3          | Standby mode                                      | 45       |

| 6.1.4          | Sleep mode                                        | 46       |

| 6.2            | Resets                                            | 47       |

| 6.2.1          | Initial reset from the Power-On-Circuit           | 49       |

| 6.2.2          | External Reset from the RESET pin                 | 49       |

| 6.2.3          | PortA programmed Reset combination.               | 49       |

| 6.2.4          | Watch-Dog timer Reset                             | 49       |

| 6.2.5          | BusError reset                                    | 49       |

| 6.2.6          | Reset Registers                                   | 49       |

| 6.2.7          | Oscillators and prescaler control                 | 50       |

| 6.2.8          | Other features                                    | 50       |

| 6.3            | Interrupt                                         | 50       |

| 6.3.1          | Features                                          | 50       |

| 6.3.2          | Overview                                          | 51       |

| 6.3.3          | PortA interrupts                                  | 51       |

| 6.3.4          | Counters A, B, C and D interrupts                 | 51       |

| 6.3.5          | Prescaler interrupts                              | 51       |

| 6.3.6          | Voltage Level Detector interrupt                  | 52       |

| 6.3.7          | Acquisition chain interrupt                       | 52       |

| 6.3.8          | Interrupt priorities                              | 52       |

| 6.4            | Events                                            | 54       |

| 6.4.1          | Features                                          | 54       |

| 6.4.2          | Overview                                          | 55       |

| 6.4.3          | PortA events                                      | 55       |

| 6.4.4<br>6.4.5 | Counters A, B, C and D events<br>Prescaler events | 55<br>55 |

| 6.4.5<br>6.4.6 | Event priorities                                  | 55       |

| 6.5            | Miscellaneous                                     | 57       |

| 6.5.1          | Port configuration reset                          | 57       |

| 6.5.2          | Prescaler interrupt synchronization               | 57       |

| 6.6            | Digital debouncer                                 | 58       |

| 6.6.1          | Description                                       | 58       |

| 6.7            | System peripheral addresses                       | 58       |

| 0.7            | System peripheral addresses                       | 50       |

| 7 Oso          | cillators                                         | 59       |

| 7.1            | RC Oscillator                                     | 59       |

| 7.1.1          | RC oscillator principle                           | 59       |

| 7.1.2          | RC divider cold start                             | 60       |

| 7.2            | Xtal Oscillator                                   | 61       |

| 7.2.1          | General description                               | 61       |

| 7.2.2          | Typical external component                        | 61       |

| 7.2.3          | Xtal divider cold start                           | 61       |

| 7.2.4          | Description                                       | 61       |

| 7.3          | External clock                                 | 62       |

|--------------|------------------------------------------------|----------|

| 7.4          | Oscillators control                            | 62       |

| 7.4.1        | CPU clock                                      | 62       |

| 7.4.2        | Oscillator register                            | 63       |

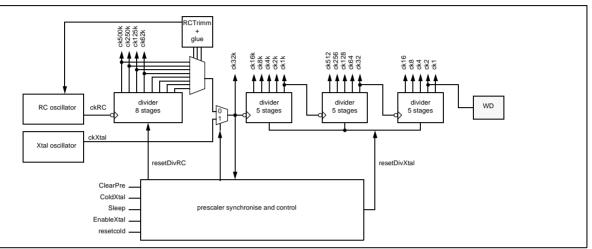

| 7.5          | Prescaler                                      | 63       |

| 7.5.1        | Features                                       | 63       |

| 7.5.2        | Description                                    | 64       |

| 7.5.3        | Registers                                      | 65       |

|              | llel IO ports                                  | 67       |

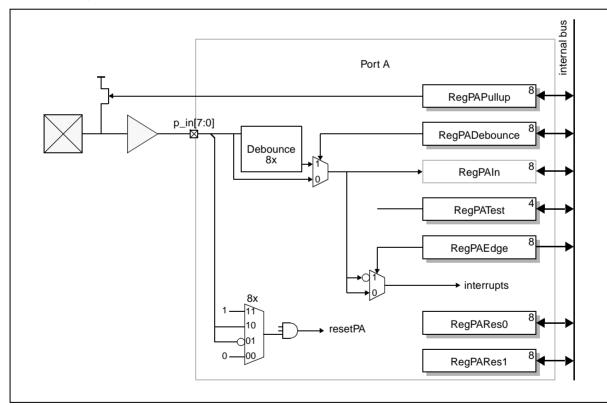

| 8.1          | Port A                                         | 67       |

| 8.1.1        | Features                                       | 67       |

| 8.1.2        | Overview                                       | 67       |

| 8.1.3        | Port A configuration                           | 67       |

| 8.1.4<br>8.2 | PortA registers<br>Port B                      | 69<br>70 |

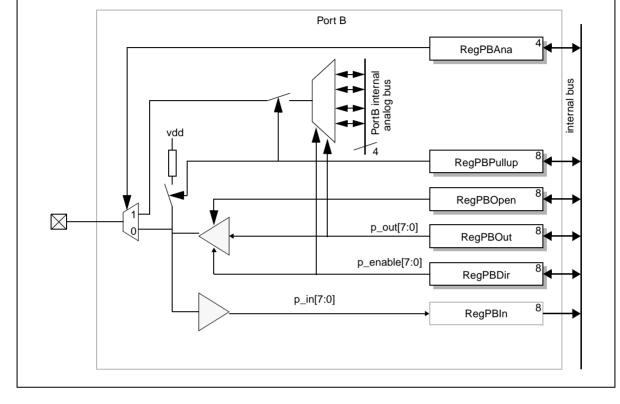

| 8.2.1        | Features                                       | 70<br>70 |

| 8.2.1        | Overview                                       | 70       |

| 8.2.3        | Port B digital capabilities                    | 70       |

| 8.2.4        | Port B analog capability                       | 72       |

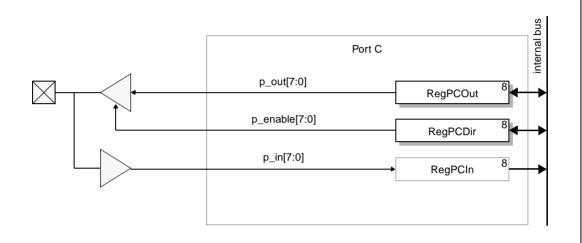

| 8.3          | Port C                                         | 73       |

| 8.3.1        | Features                                       | 73       |

| 8.3.2        | Overview                                       | 73       |

| 8.3.3        | Port D                                         | 75       |

| 9 Univ       | ersal Asynchronous Receiver/Transmitter (UART) | 77       |

| 9.1          | Features                                       | 77       |

| 9.2          | Overview                                       | 77       |

| 9.3          | Uart Prescaler                                 | 77       |

| 9.4          | Function description                           | 77       |

| 9.5          | Interrupt or polling                           | 78       |

| 9.6          | Software hints                                 | 78       |

| 10 Univ      | versal Synchronous Receiver/Transmitter (USRT) | 83       |

| 10.1         | Overview                                       | 83       |

| 10.1.1       | Enabling the serial interface                  | 83       |

| 10.1.2       | Reading the serial interface                   | 83       |

| 10.2         | Registers                                      | 83       |

| 11 Cou       | nters/timers                                   | 85       |

| 11.1         | Introduction                                   | 85       |

| 11.2         | Watchdog                                       | 85       |

| 11.3         | Counters                                       | 85       |

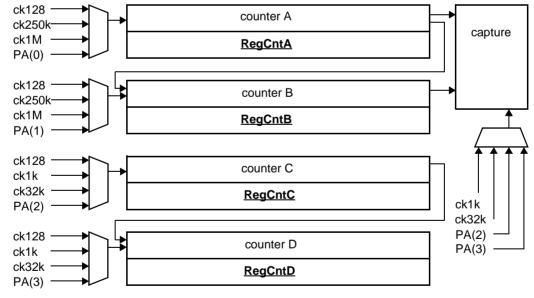

| 11.3.1       | Overview                                       | 85       |

| 11.3.2       | Features                                       | 86       |

| 11.3.3       | Block schematics                               | 86       |

| 11.3.4       | Counter Registers                              | 86       |

| 11.3.5       | Clock selection                                | 87       |

| 11.3.6       | 16 bit counters                                | 88       |

| 11.3.7           | Up/down counting                             | 89         |

|------------------|----------------------------------------------|------------|

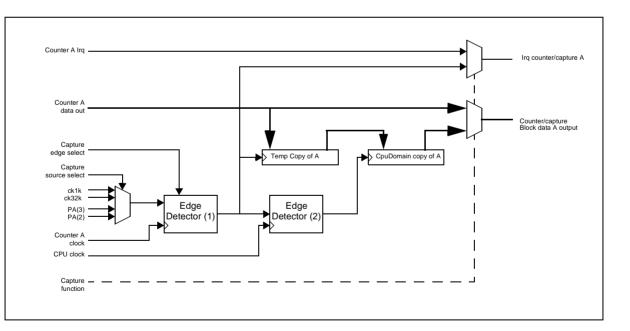

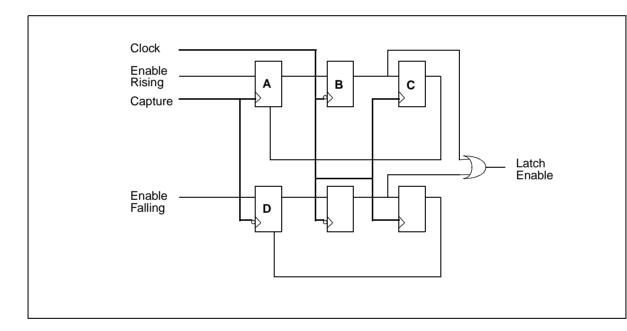

| 11.3.8           | Capture functions                            | 90         |

| 11.3.9           | PWM functions                                | 92         |

| 11.3.10          | Counter registers                            | 94         |

| 12 Vo            | Itage Level Detector                         | 97         |

| 12.1             | Features                                     | 97         |

| 12.2             | Overview                                     | 97         |

| 12.3             | VLD operation                                | 97         |

| 12.4             | Registers                                    | 98         |

| 13 Pov           | wer-on reset                                 | 99         |

| 14 Ac            | quisition chain                              | 101        |

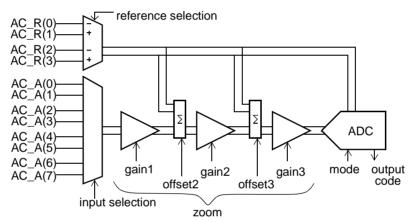

| 14.1             | Introduction                                 | 101        |

| 14.2             | Block diagram                                | 101        |

| 14.3             | Input signal multiplexing                    | 101        |

| 14.4             |                                              | 101        |

|                  | Input reference multiplexing                 |            |

| 14.5             | Amplifier chain                              | 102        |

| 14.5.1<br>14.5.2 | PGA 1<br>PGA2                                | 103        |

| 14.5.2           | PGA2<br>PGA3                                 | 103<br>104 |

| 14.6             | ADC                                          | 104        |

| 14.6.1           | Input-Output relation                        | 104        |

| 14.6.2           | Operation mode                               | 104        |

| 14.6.3           | Conversion sequence                          | 104        |

| 14.6.4           | Conversion duration                          | 105        |

| 14.6.5           | Resolution                                   | 105        |

| 14.6.6           | ADC performances                             | 105        |

| 14.7             | Control part                                 | 106        |

| 14.7.1           | Starting a convertion                        | 106        |

| 14.7.2           | Clocks generation                            | 106        |

| 14.7.3           | Default operation mode (not yet implemented) | 106        |

| 14.7.4           | Registers                                    | 106        |

| 14.8             | Acquisition of a sample                      | 108        |

| 15 An            | alog outputs                                 | 109        |

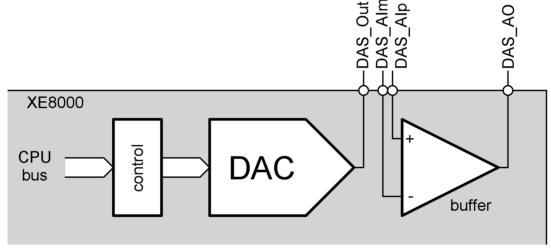

| 15.1             | Signal DAC                                   | 109        |

| 15.1.1           | Application                                  | 109        |

| 15.1.2           | Typical external components                  | 109        |

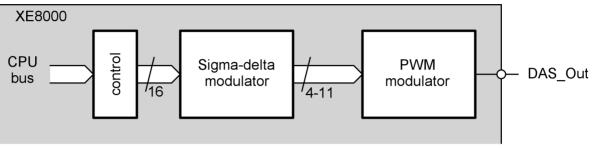

| 15.1.3           | Block diagram                                | 109        |

| 15.1.4           | The generic DAC                              | 110        |

| 15.1.5           | The amplifier                                | 110        |

| 15.1.6           | Signal DAC registers                         | 111        |

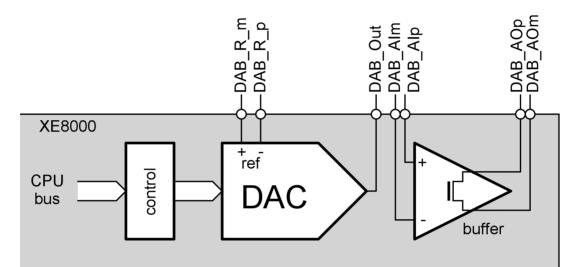

| 15.2             | Bias DAC                                     | 113        |

| 15.2.1           | Application                                  | 113        |

| 15.2.2           | Typical external components                  | 113        |

| 15.2.3<br>15.2.4 | Block diagram<br>The DAC                     | 113<br>113 |

| 13.2.4           |                                              | 115        |

| 1:   | 5.2.5 The amplifier                            | 113 |

|------|------------------------------------------------|-----|

| 1:   | 5.2.6 Bias DAC registers                       | 114 |

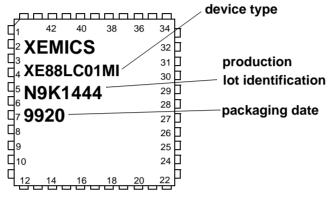

| 16   | Pin-out, package and electrical specifications | 115 |

| 16.1 |                                                | 115 |

| 16.2 | 1                                              | 117 |

| 16.2 |                                                | 119 |

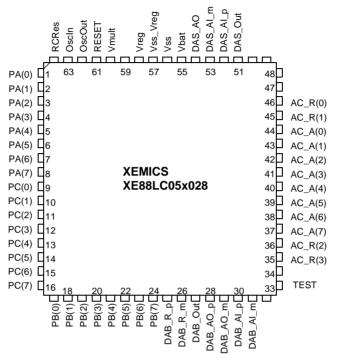

| 16.3 | XE88LC05 pin-out                               | 119 |

| 16.4 | -                                              | 121 |

| 10   | 6.4.1 Absolute maximum ratings                 | 121 |

| 1    | 6.4.2 Operating conditions                     | 121 |

| 10   | 6.4.3 IO pins operation                        | 121 |

| 17   | Index                                          | 123 |

| 18   | Contact                                        | 125 |

| +     |  |

|-------|--|

|       |  |

| VV    |  |

|       |  |

|       |  |

|       |  |

|       |  |

|       |  |

| U     |  |

|       |  |

|       |  |

|       |  |

|       |  |

|       |  |

|       |  |

|       |  |

|       |  |

| 2     |  |

|       |  |

| ary   |  |

| a     |  |

|       |  |

| a     |  |

| nal   |  |

| imina |  |

| imina |  |

| imina |  |

| imina |  |

XX-XE88LC01/03/05, Data Book

# Preliminary information

# List of figures

|                                                                                     | 10       |

|-------------------------------------------------------------------------------------|----------|

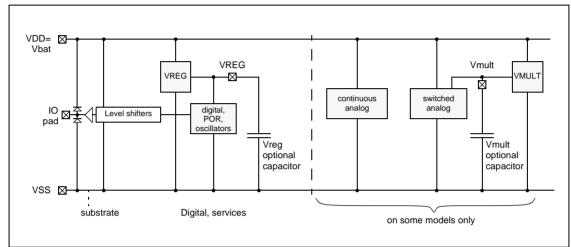

| Figure 3.1: Power supply strategy.                                                  | 19       |

| Figure 3.2: Selection of the operation mode with respect to the power supply range. | 19       |

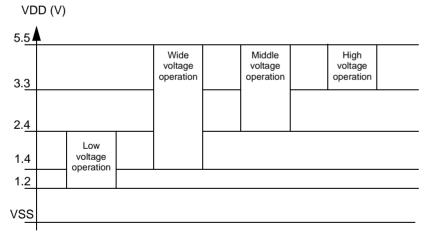

| Figure 3.3: b) Power supply connection for wide voltage operation.                  | 20       |

| Figure 3.3: a) Power supply connection for low voltage operation.                   | 20       |

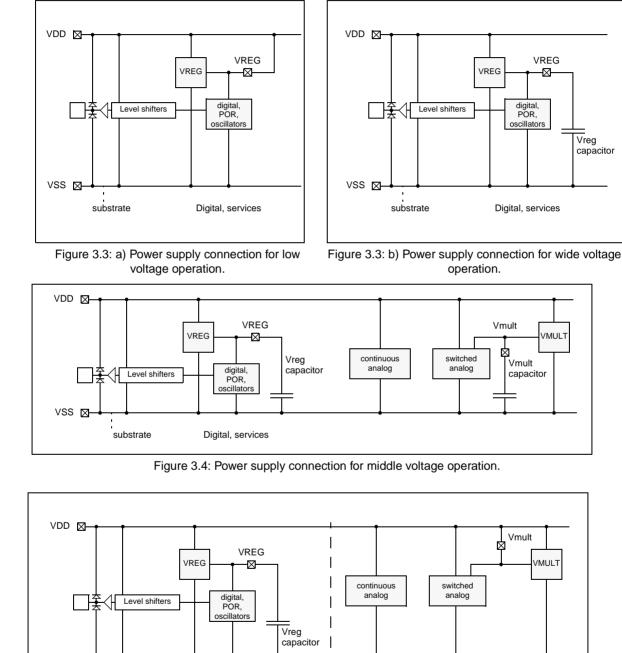

| Figure 3.4: Power supply connection for middle voltage operation.                   | 20       |

| Figure 3.5: Power supply connection for high voltage operation.                     | 20       |

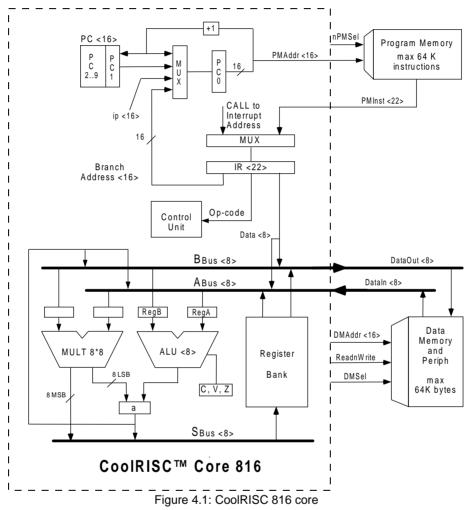

| Figure 4.1: CoolRISC 816 core                                                       | 23       |

| Figure 4.2: CoolRISC Pipeline                                                       | 24       |

| Figure 4.3: Pipeline execution of different instructions                            | 25       |

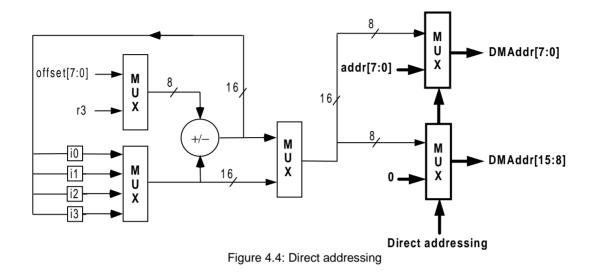

| Figure 4.4: Direct addressing                                                       | 33       |

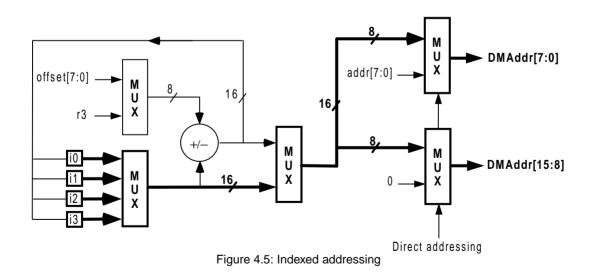

| Figure 4.5: Indexed addressing                                                      | 33       |

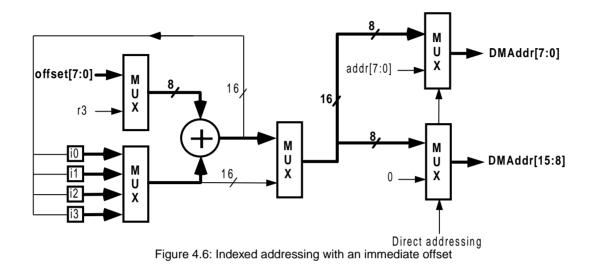

| Figure 4.6: Indexed addressing with an immediate offset                             | 34       |

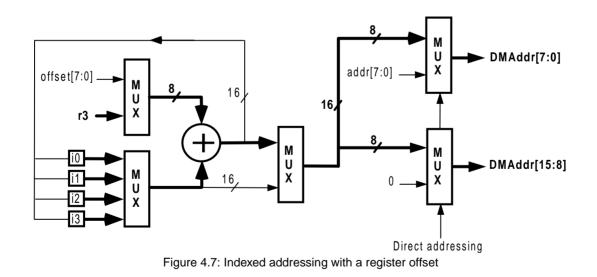

| Figure 4.7: Indexed addressing with a register offset                               | 34       |

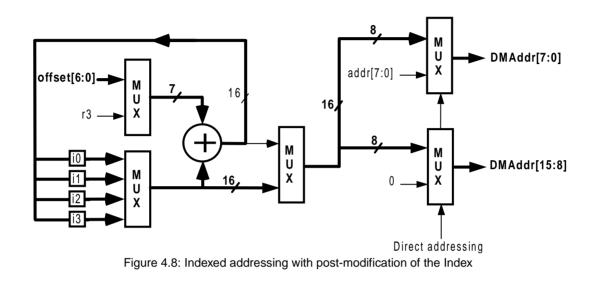

| Figure 4.8: Indexed addressing with post-modification of the Index                  | 35       |

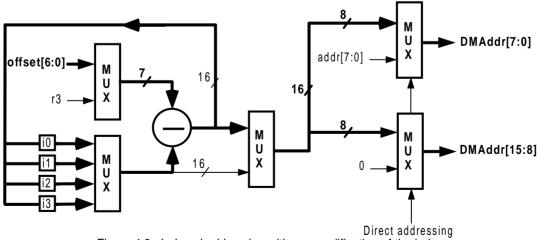

| Figure 4.9: Indexed addressing with pre-modification of the index                   | 35       |

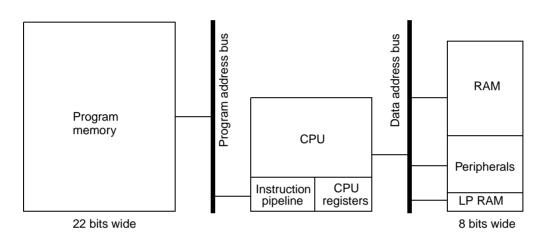

| Figure 5.1: Memory organization                                                     | 41       |

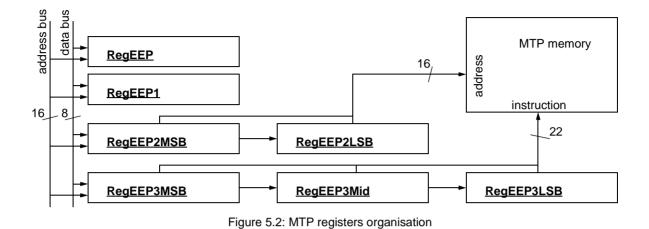

| Figure 5.2: MTP registers organisation                                              | 43       |

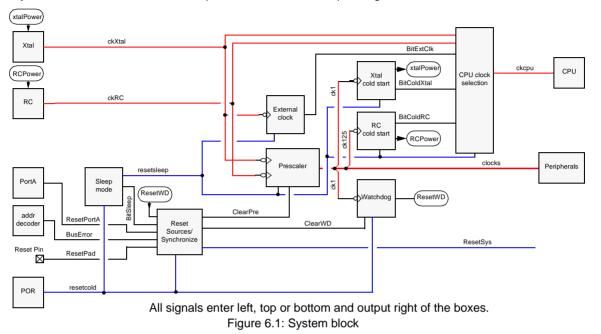

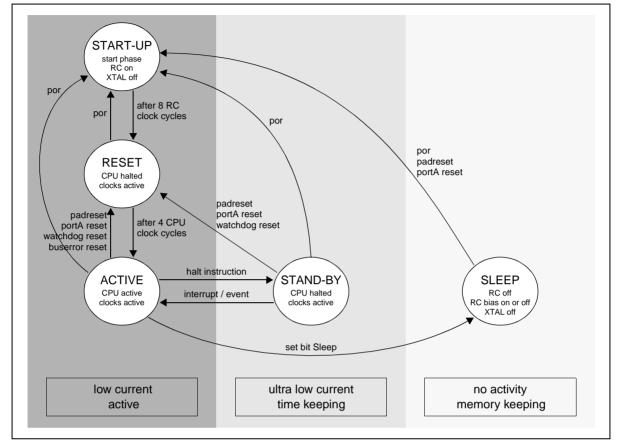

| Figure 6.1: System block                                                            | 45       |

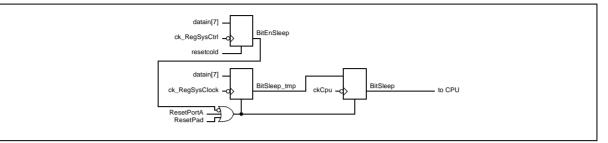

| Figure 6.2: sleep mode structure                                                    | 46       |

|                                                                                     |          |

| Figure 6.4: power-on reset start                                                    | 48       |

| Figure 6.5: wake from sleep (short reset)                                           | 48       |

| Figure 6.6: wake from sleep (long reset)                                            | 48       |

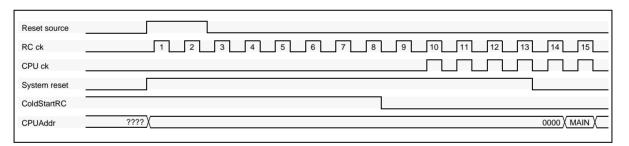

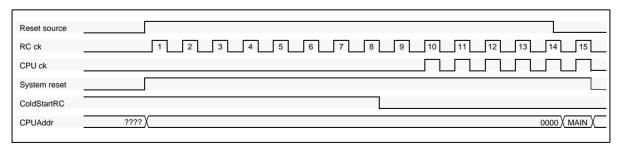

| Figure 6.7: reset in active mode                                                    | 49       |

| •                                                                                   | 49<br>57 |

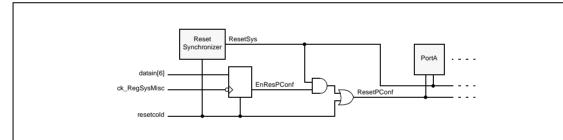

| Figure 6.8: Port configuration reset                                                |          |

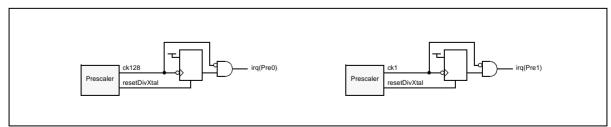

| Figure 6.9: Prescaler interrupt synchronization                                     | 57       |

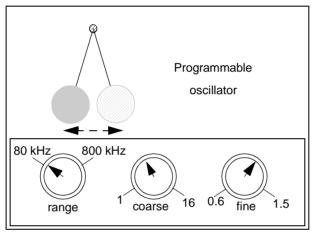

| Figure 7.1: RC programming principle                                                | 59       |

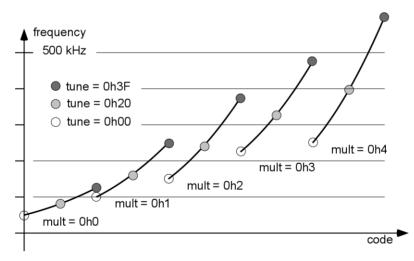

| Figure 7.2: RC frequencies programming example for low range (typical values)       | 59       |

| Figure 7.3: CPU clock selection                                                     | 63       |

| Figure 7.4: prescaler principle                                                     | 64       |

| Figure 8.1: Port A                                                                  | 67       |

| Figure 8.2: digital debouncer                                                       | 68       |

| Figure 8.3: Port B                                                                  | 70       |

| Figure 8.4: Port C                                                                  | 74       |

| Figure 9.1: example of UART messages                                                | 79       |

| Figure 11.1: Counters/timers block schematics                                       | 86       |

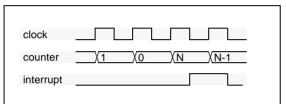

| Figure 11.2: start synchronization                                                  | 88       |

| Figure 11.3: interrupt generation                                                   | 88       |

| Figure 11.4: counter examples                                                       | 90       |

| Figure 11.5: Capture Architecture (counter A)                                       | 90       |

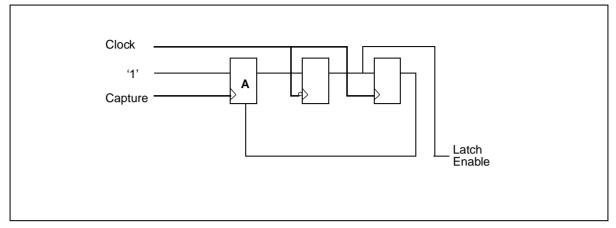

| Figure 11.6: Edge detector (1) principle                                            | 91       |

| Figure 11.7: Edge detector (2) principle                                            | 92       |

| Figure 11.8: PWM output examples                                                    | 93       |

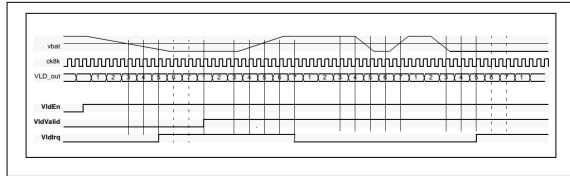

| Figure 12.1: VLD timing                                                             | 97       |

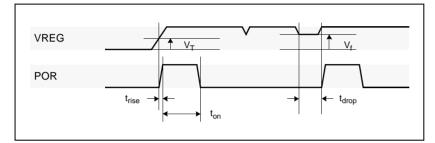

| Figure 13.1: reset conditions                                                       | 99       |

|                                                                                     |          |

| Figure 14.1: Acquisition channel block diagram with ZoomingADC <sup>TM</sup> | 101 |

|------------------------------------------------------------------------------|-----|

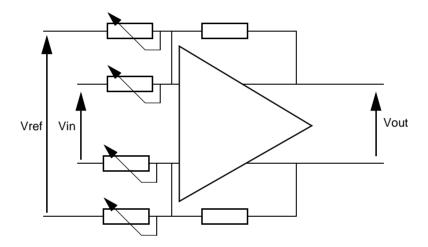

| Figure 14.2: PGA stage principle implementation                              | 103 |

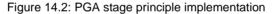

| Figure 14.3: Conversion sequence. smax is the oversampling rate.             | 105 |

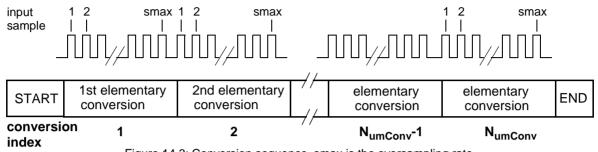

| Figure 14.4: Acquisition flow                                                | 108 |

| Figure 15.1: General block diagram                                           | 109 |

| Figure 15.2: The DAC signal structure                                        | 110 |

| Figure 15.3: General block diagram of the bias DAC                           | 113 |

| 16.1 Pinout of the XE88LC01 in TQFP44 package                                | 115 |

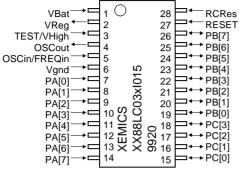

| 16.2 Pinout of the XX-XE88LC03 in SOP28 package                              | 117 |

| 16.2 Pinout of the XX-XE88LC03 in TQFP32 package                             | 117 |

| Figure 16.1: Pinout of the XE88LC05 in TQFP64 package                        | 119 |

### XX-XE88LC01/03/05, Data Book

# List of tables

| Table 1.1: access code convention                           | 15 |

|-------------------------------------------------------------|----|

| Table 2.1: List of the XE8000 family members functions      | 18 |

| Table 3.1: Voltage Regulator specifications for ROM         | 21 |

| Table 3.2: Voltage Regulator specifications for MTP         | 21 |

| Table 3.3: RegVmultCfg0                                     | 21 |

| Table 3.4: Vmult specifications                             | 21 |

| Table 3.5: Current requirement of the XE8000 family members | 22 |

| Table 4.1: CoolRISC core main characteristics               | 26 |

| Table 4.2: CoolRISC 816 Instruction Set                     | 28 |

| Table 4.3: CoolRISC 816 addressing modes                    | 30 |

| Table 4.4: CoolRISC 816 conditional jump (Jcc) conditions   | 30 |

| Table 4.5: CoolRISC 816 instruction construction            | 30 |

| Table 4.7: CoolRISC 816 registers organization              | 31 |

| Table 4.8: CoolRISC 816 interrupts                          | 31 |

| Table 4.6: CoolRISC 816 internal registers                  | 31 |

| Table 4.9: Registers Roles                                  | 32 |

| Table 4.10: Branch Conditions                               | 37 |

| Table 4.11: CALL addresses and priorities                   | 38 |

| Table 5.1: Program addresses                                | 41 |

| Table 5.2: RAM addresses                                    | 42 |

| Table 5.3: Peripherals addresses                            | 42 |

| Table 5.4: MTP Registers                                    | 43 |

| Table 6.1: System registers                                 | 47 |

| Table 6.2: EnResPConf                                       | 49 |

| Table 6.3: RegSysReset                                      | 50 |

| Table 6.4: RegSysCtrl                                       | 50 |

| Table 6.5: Debouncer frequency                              | 50 |

| Table 6.6: RegSysMisc                                       | 50 |

| Table 6.7: all interrupts and their priorities              | 52 |

| Table 6.8: Interrupt registers                              | 52 |

| Table 6.9: RegIrqHig                                        | 53 |

| Table 6.10: RegIrqMid                                       | 53 |

| Table 6.11: RegIrqLow                                       | 53 |

| Table 6.12: RegIrqEnHig                                     | 53 |

| Table 6.13: RegIrqEnMid                                     | 54 |

| Table 6.14: RegIrqEnLow                                     | 54 |

| Table 6.15: RegIrqPriority                                  | 54 |

| Table 6.16: RegIrqIrq                                       | 54 |

| Table 6.17: RegIrqTest                                      | 54 |

| Table 6.18: all events and their priorities                 | 56 |

| Table 6.19: Event registers                                 | 56 |

| Table 6.20: RegEvn                                          | 56 |

| Table 6.21: RegEvnEn                                        | 56 |

| Table 6.22: RegEvnPriority                                  | 56 |

| Table 6.23: RegEvnEvn                                       | 57 |

| Table 6.24: RegEvnTest                                                                        | 57    |

|-----------------------------------------------------------------------------------------------|-------|

| Table 6.25: Port config reset                                                                 | 57    |

| Table 6.26: Debouncer frequency                                                               | 58    |

| Table 6.27: system address ranges                                                             | 58    |

| Table 7.1: RC specifications                                                                  | 60    |

| Table 7.2: RegSysRCTrim1                                                                      | 60    |

| Table 7.3: RegSysRCTrim2                                                                      | 60    |

| Table 7.4: Xtal oscillator specifications.                                                    | 61    |

| Table 7.5: External crystal specifications. 32 kHz Xtal outside these specifications will r   | nust  |

| probably delivers correct frequency, but some precision specifications will be released.      | 61    |

| Table 7.6: Board design specifications                                                        | 61    |

| Table 7.7: CPU clock selection                                                                | 62    |

| Table 7.8: RegSysClock, address h0012                                                         | 63    |

| Table 7.9: frequency examples, typical values for RC setting, range is set to 1               | 64    |

| Table 7.10: automatic input frequency selection, typical values. Values in italic are not all | lowed |

| and may result in unpredictable CPU behaviour.                                                | 65    |

| Table 7.11: RegSysPre0                                                                        | 65    |

| Table 8.1: reset selection for each pin                                                       | 68    |

| Table 8.2: clock inputs for counters                                                          | 68    |

| Table 8.3: Port A registers                                                                   | 69    |

| Table 8.4: Register RegPAIn                                                                   | 69    |

| Table 8.5: Register RegPADebounce                                                             | 69    |

| Table 8.6: Register RegPAEdge                                                                 | 69    |

| Table 8.7: Register RegPAPullup                                                               | 69    |

| Table 8.8: RegPARes0                                                                          | 69    |

| Table 8.9: RegPARes1                                                                          | 69    |

| Table 8.10: RegPATest                                                                         | 69    |

| Table 8.11: different PortB functions                                                         | 71    |

| Table 8.12: selection for analog lines with RegPBDir (pads B0, B2, B4 and B6) or RegP         | Bout  |

| (pads B1, B3, B5 and B7)                                                                      | 72    |

| Table 8.13: Port B registers                                                                  | 72    |

| Table 8.14: RegPBIn                                                                           | 72    |

| Table 8.15: RegPBOpen                                                                         | 72    |

| Table 8.16: RegPBAna                                                                          | 73    |

| Table 8.17: RegPBPullup                                                                       | 73    |

| Table 8.18: RegPBOut                                                                          | 73    |

| Table 8.19: RegPBDir                                                                          | 73    |

| Table 8.20: Port C registers                                                                  | 74    |

| Table 8.21: RegPCOut                                                                          | 74    |

| Table 8.22: RegPCIn                                                                           | 74    |

| Table 8.23: RegPCDir                                                                          | 75    |

| Table 9.1: RC frequencies for Uart                                                            | 77    |

| Table 9.2: uart internal prescaler                                                            | 77    |

| Table 9.3: baud rate selection                                                                | 79    |

| Table 9.4: word length                                                                        | 79    |

|                                                                                               |       |

| Table 9.5: parity mode                       | 79  |

|----------------------------------------------|-----|

| Table 9.6: parity enable                     | 79  |

| Table 9.7: UART registers                    | 80  |

| Table 9.8: echo modes                        | 80  |

| Table 9.9: RegUartCmd                        | 80  |

| Table 9.10: RegUartCtrl                      | 80  |

| Table 9.11: RegUartRx                        | 80  |

| Table 9.12: RegUartRxSta                     | 80  |

| Table 9.13: RegUartTx                        | 80  |

| Table 9.14: RegUartTxSta                     | 81  |

| Table 10.1: serial interface registers       | 83  |

| Table 10.2: RegUSRTSIN                       | 83  |

| Table 10.3: RegUSRTSCL                       | 84  |

| Table 10.4: RegUSRTCtrl                      | 84  |

| Table 10.5: RegUSRTData                      | 84  |

| Table 10.6: RegUSRTEdgeSCL                   | 84  |

| Table 11.1: RegSysWD                         | 85  |

| Table 11.2: clock source for Counter A       | 87  |

| Table 11.3: clock source for Counter B       | 87  |

| Table 11.4: clock source for Counter C       | 87  |

| Table 11.5: clock source for Counter D       | 87  |

| Table 11.6: cascading counter A & B          | 88  |

| Table 11.7: cascading counter C & D          | 89  |

| Table 11.8: selection for up/down-counting   | 89  |

| Table 11.9: capture source                   | 92  |

| Table 11.10: capture function selection      | 92  |

| Table 11.11: PWM1                            | 93  |

| Table 11.12: PWM0                            | 93  |

| Table 11.13: PWM1 size selection             | 93  |

| Table 11.14: PWM0 size selection             | 93  |

| Table 11.15: Counters registers              | 94  |

| Table 11.16: RegCntA                         | 94  |

| Table 11.17: RegCntB                         | 94  |

| Table 11.18: RegCntC                         | 94  |

| Table 11.19: RegCntD                         | 94  |

| Table 11.20: RegCntCtrlCk                    | 94  |

| Table 11.21: RegCntConfig1                   | 94  |

| Table 11.22: RegCntConfig2                   | 94  |

| Table 11.23: RegCntOn                        | 95  |

| Table 12.1: Voltage level detector operation | 97  |

| Table 12.2: RegVldCtrl                       | 98  |

| Table 12.3: RegVldStat                       | 98  |

| Table 13.1: POR specifications               | 99  |

| Table 14.1: AMUX selection                   | 102 |

| Table 14.2: PGA1 Performances                | 103 |

Preliminary information

| Table 14.3: PGA2 Performances                                | 103 |

|--------------------------------------------------------------|-----|

| Table 14.4: PGA3 Performances                                | 104 |

| Table 14.5: ADC Performances                                 | 105 |

| Table 14.6: Peripheral register memory map                   | 106 |

| Table 14.7: Peripheral register memory map, bits description | 107 |

| Table 15.1: DAC signal amplifier performances                | 110 |

| Table 15.2: Signal DAC registers                             | 111 |

| Table 15.3: RegDasCfg0                                       | 111 |

| Table 15.4: RegDasCfg1                                       | 111 |

| Table 15.5: Noise shaping setting                            | 111 |

| Table 15.6: PWM setting                                      | 111 |

| Table 15.7: DAC status                                       | 111 |

| Table 15.8: Clock setting                                    | 112 |

| Table 15.9: PWM polarity                                     | 112 |

| Table 15.10: DAC performances                                | 113 |

| Table 15.11: Amplifier performances                          | 113 |

| Table 15.12: Bias DAC registers                              | 114 |

| Table 15.13: RegDab1Cfg                                      | 114 |

| 16.1 Pin-out of the XX-XE88LC01 in TQFP44                    | 115 |

| 16.2 Pin-out of the XX-XE88LC03 in SO28 and TQFP32           | 117 |

| Table 16.1: Pin-out of the XE88LC05 in TQFP64                | 119 |

| Table 16.2: Absolute maximum ratings                         | 121 |

| Table 16.3: Operating conditions                             | 121 |

| Table 16.4: IO pins performances                             | 121 |

# **1** Introduction

The XE8000 is a family of microcontrollers (MCU) characterised by their very low power requirement. These MCUs are perfectly adapted to manage systems working on batteries or remotely powered.

The XE8000 is conceived as an evolutionary family of MCU that can address many applications. As there are always applications that can not be covered by such a product line, XEMICS also offers full custom ASICs based on the XE8000, including additional peripherals on request. The intellectual property that the XE8000 relies on, as well as the low power digital libraries, are available from XEMICS.

This document describes the functional components of the XE8000 family and their performance. Additional information relative to specific applications is available as "Application Notes".

### 1.1 Conventions used in this document

The negative power supply is named VSS. VSS is internally connected to the substrate of the chip. Unless otherwise stated, all voltages are given with respect to VSS.

Current is positive when flowing into a pin. This pin is said to be "sinking" current. When the current is going out of the chip, its value is negative and the pin is said "sourcing" current.

All digital words are written from MSB to LSB (MSB left, LSB right). These words are expressed with all their digits either in binary, decimal or hexadecimal format. When expressed in binary, the word has a "b" at its beginning, when expressed in decimal, the word has nothing or a "d" at its beginning, when expressed in hexadecimal, the word has an "h" at its beginning.

Unless otherwise stated, all digital signals are active high.

**<u>RegSystem</u>** this is a register

**EnableRC** this is a bit in a register

An unreadable bit will output 0 when read.

| code | bit (register) read-write access       |

|------|----------------------------------------|

| r    | readable                               |

| w    | write able                             |

| c1   | readable, cleared by writing 1         |

| С    | readable, cleared by writing any value |

Table 1.1: access code convention

Sometimes the abbreviation for "micro-" is "u" instead of " $\mu$ ".

1 Introduction

# 2 XE8000 MCU Family

### 2.1 Features

The main characteristics of the XE8000 MCU family are

- Ultra low power operation

- Low voltage operation (1.2 V or 2.4 V to 5.5 V)

- High efficiency CPU

- 1 instruction per clock cycle, for all instructions

- 22 bits wide instructions

- Integrated 8x8 -> 16 bits multiplier

- 8 bit data bus

- 64k instruction program addressing space

- 64kB data addressing space

- 8 addressing modes

- MTP (multiple time programmable) memory available

- Dual clock (X-tal and/or RC)

- Each peripheral can be set on/off individually for minimal power consumption

- UART and synchronous serial interface

- Watch dog

- Four 8 bit timers with PWM ability

- Advanced acquisition path

- Fully differential analog signal path for signal and reference

- 4x2 or 7x1 + 1 signal input

- 2x2 reference input

- 0.5 1000 programmable gain amplifier

- Offset programmed over +- 10 full scale

- 5 16 bits resolution ADC

- Low speed modes with reduced bias current for minimal power consumption

- Bias and signal DACs for resistive bridge sensing and analog output

- Complete development tools using Windows 95 or NT graphical interface

- Assembler

- ANSI-C compiler

- Source level debugger

- CPU Simulator

- CPU Emulator XE8000HaCE

- Starter kits (in preparation)

- Programmer (ProStart, includes an eval board)

- Hardware emulators (works with XE8000HaCE, in preparation)

### 2.2 Family

The XE8000 Family ultra low-power microcontroller is made up of several members, all using the same microprocessor core and differing by the peripherals available.

The XE88LC01 is a low-power sensing microcontroller, based on the XE88LC01, with an advanced acquisition path including diferential programmable gain amplifiers and a high resolution analog to digital converter. Its main applications are dataloggers and process control.

The XE88LC02 is a low-power sensing microcontroller, based on the XE88LC01, with an additionnal LCD driver. Its main applications are metering and dataloggers.

The XE88LC03 is a low-power, low-voltage, general purpose microcontroller. Its main features are the very efficient CoolRISC core, the low voltage function and the real time clock. Its main applications are low voltage control and supervision. XE88LC03 will be superseeded by the XE88LC06 later this year.

The XE88LC04 is a low-power, low-voltage, general purpose microcontroller, based on the XE88LC03, with an additionnal LCD driver. Its main features are the very efficient CoolRISC core, the low voltage function and the real time clock. Its main applications are low voltage control and supervision.

The XE88LC05 is a low power sensing microcontroller, based on the XE88LC01, with analog outputs. Its main applications are piezoresistive sensors and 4 - 20 mA loops systems.

Other microcontrollers derived from the XE8000 family members can be produced on request, either as new standard products or as customer specific circuits.

|                                                   | XE88LC01                                                                 | XE88LC02                                                                 | XE88LC03                                                                 | XE88LC04                                                                 | XE88LC05                                                                    | XE88LC06                                                                 |

|---------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Supply voltage                                    | 2.7 - 5.5 V                                                              | 2.4 - 5.5 V                                                              | 2.7 - 5.5 V                                                              | 1.2- 5.5 V for<br>ROM<br>2.4 - 5.5 V for<br>MTP                          | 2.7 - 5.5 V                                                                 | 1.2- 5.5 V for<br>ROM<br>2.4 - 5.5 V for<br>MTP                          |

| Max speed                                         | 2 MIPS                                                                   | 4 MIPS                                                                   | 2 MIPS                                                                   | 4 MIPS at 2.4 V                                                          | 2 MIPS                                                                      | 4 MIPS at 2.4 V                                                          |

| Operating<br>temperature                          | -40 - 85 °C                                                              | -40 - 85 °C<br>-40 - 125 °C                                              | -40 - 85 °C                                                              | -40 - 85 °C                                                              | -40 - 85 °C                                                                 | -40 - 85 °C<br>-40 - 125 °C                                              |

| CPU                                               | CoolRISC 816,<br>22 bits<br>instructions<br>8 bits data<br>HW multiplier    | CoolRISC 816,<br>22 bits<br>instructions<br>8 bits data<br>HW multiplier |

| Program memory                                    | 8k Instructions<br>= 22 kB MTP                                           | 8k Instruction<br>= 22 kB MTP or<br>6k Intructions<br>= 16 kB ROM        | 8k Instructions<br>= 22 kB MTP                                           | 8k Instructions<br>= 22 kB MTP or<br>6k Intructions<br>= 16 kB ROM       | 8k Instructions<br>= 22 kB MTP                                              | 8k Instructions<br>= 22 kB MTP or<br>6k Intructions<br>= 16 kB ROM       |

| Data memory                                       | 512 + 8 Bytes                                                            | 768 + 8 Bytes                                                            | 512 + 8 Bytes                                                            | 768 + 8 Bytes                                                            | 512 + 8 Bytes                                                               | 512 + 8 Bytes                                                            |

| Port A                                            | 8 input and<br>external interrupt                                           | 8 input and<br>external interrupt                                        |

| Port B                                            | 8 input/output and<br>analog                                             | 8 input/output and analog                                                | 8 input/output and<br>analog                                             | 8 input/output and<br>analog                                             | 8 input/output and<br>analog                                                | 8 input/output and<br>analog                                             |

| Port C                                            | 8 input/output                                                           | 8 input/output                                                           | 4 to 8 input/output                                                      | 4 to 8 input/output                                                      | 8 input/output                                                              | 8 input/output                                                           |

| Watchdog timer                                    | yes                                                                      | yes                                                                      | yes                                                                      | yes                                                                      | yes                                                                         | yes                                                                      |

| General purpose<br>timers with PWM<br>and Capture | 4 x 8 bits                                                                  | 4 x 8 bits                                                               |

| UART                                              | yes                                                                      | yes                                                                      | yes                                                                      | yes                                                                      | yes                                                                         | yes                                                                      |

| 2-3 wires serial<br>interface                     | transition<br>detection<br>+ software                                       | transition<br>detection<br>+ software                                    |

| Voltage level<br>detector                         | yes                                                                      | yes                                                                      | yes                                                                      | yes                                                                      | yes                                                                         | yes                                                                      |

| Oscillators                                       | 32 kHz quartz,<br>internal RC                                               | 32 kHz quartz,<br>internal RC                                            |

| LCD drivers                                       |                                                                          | 120 segments                                                             |                                                                          | 120 segments                                                             |                                                                             |                                                                          |

| Analog mux                                        | Port B and<br>4x2 or 7x1+1                                               | Port B and<br>4x2 or 7x1+1                                               | Port B                                                                   | Port B                                                                   | Port B and<br>4x2 or 7x1+1                                                  | Port B                                                                   |

| LP comparators                                    |                                                                          | 4                                                                        |                                                                          | 4                                                                        |                                                                             | 4                                                                        |

| PGA                                               | gain 0.5 - 1000                                                          | main 0 F 1000                                                            |                                                                          |                                                                          | gain 0.5 - 1000                                                             |                                                                          |

|                                                   | °                                                                        | gain 0.5 - 1000                                                          |                                                                          |                                                                          | •                                                                           |                                                                          |

| ADC                                               | 5 - 16 bits<br>resolution                                                | 5 - 16 bits<br>resolution                                                |                                                                          |                                                                          | 5 - 16 bits<br>resolution                                                   |                                                                          |

| -                                                 | 5 - 16 bits                                                              | 5 - 16 bits                                                              | 2 PWM                                                                    | 2 PWM                                                                    | 5 - 16 bits                                                                 | 2 PWM                                                                    |

| ADC                                               | 5 - 16 bits<br>resolution                                                | 5 - 16 bits<br>resolution                                                | 2 PWM<br>SO28, TQFP32,<br>die                                            | 2 PWM                                                                    | 5 - 16 bits<br>resolution<br>2 PWM<br>8 bit bias DAC,<br>4 - 16 bits signal | 2 PWM<br>SO28, TQFP32,<br>die                                            |

Table 2.1: List of the XE8000 family members functions

# **3** Power supply

### 3.1 In circuit power supply principle

The power supply uses two regulators (Figure 3.1), Vreg should be connected to VDD for low voltage operation, Vmult should be connected to VDD for high voltage operation. There are several operation modes depending on the voltage range of the power supply (Figure 3.2). MTP and mixed signal blocks are limited to Middle and High voltage ranges.

Figure 3.1: Power supply strategy.

Figure 3.2: Selection of the operation mode with respect to the power supply range.

Voltage for the digital and for regular service blocks when operating in wide, middle and high voltage mode is regulated below power supply to have a minimal current requirement.

An additional high-voltage is generated when operating in middle voltage for controlling the internal analog switches.

### 3.2 Voltage regulator

All digital parts are powered through the voltage regulator. An external capacitor is needed for the regulated voltage. It should be bypassed to VDD if working in low voltage mode. The Vreg output value depends on the program memory implementation.

Digital, services

VSS 🖂

substrate

Analog for some chips

| symbol             | description             | min | typ | max | unit | comments |

|--------------------|-------------------------|-----|-----|-----|------|----------|

| V <sub>REG</sub>   | regulated voltage       | 1.4 |     | 1.9 | V    |          |

| t <sub>START</sub> | start-up time           |     |     | 0.5 | ms   |          |

| C <sub>reg</sub>   | external load capacitor | 80  | 100 | 120 | nF   |          |

Table 3.1: Voltage Regulator specifications for ROM

| symbol             | description             | min | typ | max | unit | comments |

|--------------------|-------------------------|-----|-----|-----|------|----------|

| V <sub>REG</sub>   | regulated voltage       |     | 2   |     | V    |          |

| t <sub>START</sub> | start-up time           |     | tbd |     | ms   |          |

| CL                 | external load capacitor |     | tbd |     | nF   |          |

Table 3.2: Voltage Regulator specifications for MTP

### 3.3 Voltage multiplier

The Vmult block generates a voltage that is higher or equal to the supply voltage. The output voltage is intended for use in analog switch drivers, for example in the ADC and PGA block.

The voltage multiplier should be on when using switched analog blocks, like ADC, DAC or analog properties of the Port B under middle voltage conditions.

The clock source of Vmult is selected from the 2-bit register Vmult\_fin. The normal usage is with the clock frequency of the acquisition chain. Other settings are reserved. An example of setting the regulator is as follows:

MOVE RegVmultCfg0, #0b00000100; sets Vmult enable bit

An example of setting the regulator off follows:

MOVE RegVmultCfg0, #0b0000000; resets Vmult enable bit

| bit | name     | reset | rw | description                                                                                                                                            |

|-----|----------|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3 |          | 00000 | rw | reserved                                                                                                                                               |

| 2   | enable   | 0     | rw | 0: multiplier is stopped<br>1: multiplier is active                                                                                                    |

| 1-0 | fin[1:0] | 00    | rw | Clock source for Vmult:<br>00 : identical to acquisition chain clock<br>(see corresponding chapter)<br>01 : reserved<br>10 : reserved<br>11 : reserved |

### Table 3.3: RegVmultCfg0

| symbol | description        | min | typ | max | unit | comments                                                     |

|--------|--------------------|-----|-----|-----|------|--------------------------------------------------------------|

| Tsu    | start-up time      |     |     | 1   | ms   | defined as the time to reach the minimum output voltage Vout |

| Cext   | external capacitor | 1.1 | 1.8 | 2.5 | nF   |                                                              |

Table 3.4: Vmult specifications

### 3.4 Current requirement

| •••••••                                                                            | riequitement           |                        |                        |         |

|------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|---------|

| Operation conditions                                                               | XE88LC01R<br>XE88LC01M | XE88LC03R<br>XE88LC03M | XE88LC05R<br>XE88LC05M | Remarks |

| CPU running<br>at 1 MIPS                                                           | 310 uA                 | 310 uA                 | 310 uA                 | 1       |

| CPU running<br>at 32 kHz<br>on Xtal,<br>RC off                                     | 10 uA                  | 10 uA                  | 10 uA                  | 1       |

| Table 3.5: Currer                                                                  | t requirement of       | the XE8000 fami        | ly members             |         |

| CPU halt,<br>timer on Xtal,<br>RC off                                              | 1 uA                   | 1 uA                   | 1 uA                   | 1       |

| CPU halt,<br>timer on Xtal,<br>RC ready                                            | 1.7 uA                 | 1.7 uA                 | 1.7 uA                 | 1       |

| CPU halt,<br>Xtal off<br>timer on RC<br>at 100 kHz                                 | 1.4 uA                 | 1.4 uA                 | 1.4 uA                 | 1       |

| CPU halt,<br>ADC 12 bits<br>at 4 kHz,<br>PGA off                                   | 200 uA                 |                        | 200 uA                 | 1,4     |

| CPU halt,<br>ADC 12 bits<br>at 4 kHz,<br>PGA gain 100                              | 480 uA                 |                        | 480 uA                 | 1,4     |

| CPU halt,<br>LCD on,<br>timer on Xtal                                              |                        |                        |                        | 1       |

| CPU at 1 MIPS,<br>ADC 12 bits,<br>signal DAC 10 bits<br>at 4 kHz,<br>PGA off       |                        |                        | 725 uA                 | 3,4,5   |

| CPU at 1 MIPS,<br>ADC 12 bits,<br>signal DAC 10 bits<br>at 4 kHz,<br>PGA gain 10   |                        |                        | 870 uA                 | 3,4,5   |

| CPU at 1 MIPS,<br>ADC 12 bits,<br>signal DAC 10 bits<br>at 4 kHz,<br>PGA gain 100  |                        |                        | 1 mA                   | 3,4,5   |

| CPU at 1 MIPS,<br>ADC 12 bits,<br>signal DAC 10 bits<br>at 4 kHz,<br>PGA gain 1000 |                        |                        | 1.2 mA                 | 3,4,5   |

| Voltage level<br>detection                                                         | 10 uA                  | 10 uA                  | 10 uA                  | 2       |

**Note:** 1) Over 2.4 - 5.5 V, at 27 °C, max values.

**Note:** 2) Additional current, duration of the request is shorter than 2 ms.

Note: 3) Output not loaded.

Note: 4) Current requirement can be divided by a factor of 2 or 4 by reducing the speed accordingly.

Note: 5) At 2.4 V, at 27 °C, max values.

# 4 Central processing unit

### 4.1 Introduction

The XE8000 family is built around the CoolRISC 816 processor core. This is a Harvard type RISC processor (Program address is separated from data address). It is extremely efficient using large instruction words (22 bits), one clock per cycle instruction set (inclusive multiplication) and efficient pipeline.

### Pipeline

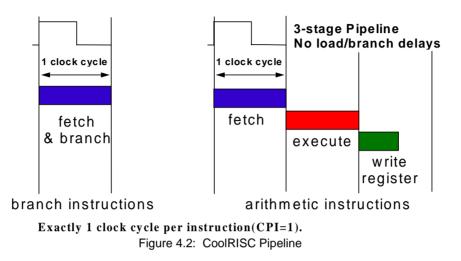

The CoolRISC architecture is based on a 3-stage pipeline. One instruction enters the pipeline at each clock cycle and executes in a maximum of 3 cycles. The CoolRISC pipeline suffers no penalty such as delay slots or branch delays present in most RISC processors. Thus the clock count per instruction (CPI) is exactly one. As a result the number of cycles needed to execute a task is easily determined, since it matches the number of executed instructions.

Figure 4.2 shows the timing diagram for the pipeline. Arithmetic instructions go through all three stages of the pipeline, thus executes in 3 clock cycles. A bypass mechanism is used to avoid any load delay[10].

4.1.1

It should be mentioned that existing 4-bit and 8-bit microprocessors typically need between 4 to 20 clocks per instruction (CPI), some newer CPU use 1 clock cycle for simple operations (MOVE) but 2 to 6 cycles for more complex operations (ADD, JPC). The efficiency of the CoolRISC architecture is far better than these microprocessors.

Figure 4.2 presents the timing diagram for the execution of different types of instructions.

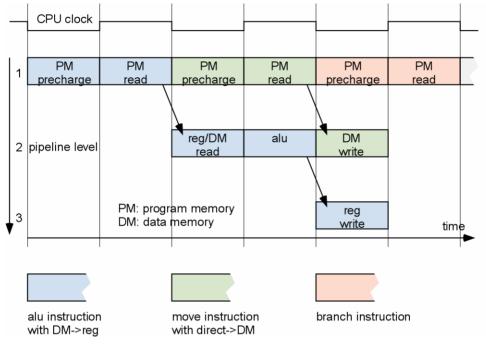

The first instruction on Figure 4.3 is a typical ALU operation with a first operand in Data Memory (DM) and a second operand in a register. The result is stored in the destination register. During the first clock cycle, the Program Memory (PM) is pre-charged in the first phase and the instruction is read and is decoded in the second phase. During the second clock cycle, the register and the DM are read in phase 3 and the ALU operation is executed in phase 4. The last clock cycle contains only a single phase (phase 5) used to store the result in the destination register.

The second instruction shown is a Data Memory store instruction. The first clock cycle is identical for all instructions. The second clock cycle contains only phase 3 in which the value of a register is written into the DM.

### XX-XE88LC01/03/05, Data Book

### 4 Central processing unit

Figure 4.3: Pipeline execution of different instructions

The last instruction shown is a branch instruction. A single clock cycle is necessary for all branch instructions (conditional or unconditional jump, call, return). During phase 2, the next Program Memory address can be determined while considering an already computed test condition (computed during phase 4 of the previous instruction, which is phase 2 of the considered branch instruction). The new address is loaded into the PC at the high-to-low transition of the clock between phase 2 and 3.

Branch instructions executed in one clock do not result in branch delays that generally degrade the pipeline performance [10]. Thus, CPI=1 is not a peak value, but rather a characteristic of the CoolRISC© architecture.

Figure 4.3 shows a Data Memory-reg ALU instruction followed by a DM store instruction. The first instruction stores its result in a register during phase 5 which is phase 3 of the DM store instruction. A bypass mechanism allows the DM store instruction to read the register that is written by the preceding ALU instruction. Such a mechanism does not require load delays.

As the CoolRISC pipeline is not affected by branch or load delays [11], the pipeline hardware is simplified (no branch prediction needs to be performed [10]). This makes the CoolRISC© pipeline very efficient and low in power.

### 4.1.2 Gated clocks

The gated clock technique has been extensively used in the CoolRISC© design. It uses the ALU with input and control registers that are loaded only when an ALU operation has to be executed. During the execution of another type of instruction (branch, store, etc...), these registers are not clocked, thus no transitions occur in the ALU. This reduces power consumption.

A similar mechanism is used for the instruction registers, thus in a branch, which is executed only in the first pipeline stage, no transitions occur in the second and third stages of the pipeline.

Gated clocks can be advantageously combined with the pipeline architecture. When input and control registers have to be implemented to obtain a gated clock ALU, they are naturally used as pipeline registers.

### 4.1.3 Low frequency modes

The processor internal frequency can be reduced by a factor of 2, 4, 8 or 16. The division factor is both hardware and software controlled.

The **FREQ** instruction sets the basic division factor which is output on the processor **FreqOut[3:0]** bus. This value can be combined with other signals in an external hardware decoder to compute the final division factor which is then input on the **FreqIn[3:0]** bus.

Power consumption can be further decreased by putting the processor in the low-power standby mode with the **HALT** instruction. It will restart when an Event or an Interrupt occurs.

### 4.1.4 Stand-by Mode

The **HALT** instruction puts the processor in standby mode in which power consumption is minimum. The clock is stopped at the entrance of the processor to prevent any transition in the core.

### 4.1.5 CoolRISC© Core Features

| CoolRISC© Core                                 | CoolRISC816 as<br>implemented in<br>XE88LC01-03-05 | Maximal CoolRISC816<br>capabilities |  |  |

|------------------------------------------------|----------------------------------------------------|-------------------------------------|--|--|

| CPI (clock per instruction)                    | 1                                                  | 1                                   |  |  |

| Pipeline                                       | 3 stages                                           | 3 stages                            |  |  |

| Branch/Load delay                              | no                                                 | no                                  |  |  |

| Data Width                                     | 8                                                  | 8                                   |  |  |

| No. of Registers                               | 8                                                  | 16                                  |  |  |

| Max. Program Memory size                       | 8k * 22 (= 22 kBytes)                              | 64k * 22 (= 360 kBytes)             |  |  |

| Max. Data Memory size                          | 512 * 8                                            | 64k * 8                             |  |  |

| Instruction size                               | 22                                                 | 22                                  |  |  |

| No. of Program Memory Index Registers          | 1                                                  | 1                                   |  |  |

| No. of Data Memory Index Registers             | 4                                                  | 4                                   |  |  |

| No. of Program Memory pages                    | 1 * 8k                                             | 1 * 64k                             |  |  |

| No. of Data Memory pages                       | 2 * 256                                            | 256 * 256                           |  |  |

| No. of Data Memory addressing modes            | 8                                                  | 8                                   |  |  |

| Software CALL (branch & link)                  | yes                                                | yes                                 |  |  |

| No. of nested hardware CALL                    | 4                                                  | 8                                   |  |  |

| No. of Interrupt Levels                        | 3                                                  | 3                                   |  |  |

| Nested Interrupts                              | yes                                                | yes                                 |  |  |

| No. of EVENT levels                            | 2                                                  | 2                                   |  |  |

| Test access                                    | serial                                             | serial                              |  |  |

| Halt mode                                      | yes                                                | yes                                 |  |  |

| 8 by 8 to 16 multiplication in one instruction | yes                                                | yes                                 |  |  |

| Barrel Shifter                                 | yes                                                | yes                                 |  |  |

| Two-Complement capabilities                    | yes                                                | yes                                 |  |  |

Table 4.1: CoolRISC core main characteristics

### 4.2 Programmer's Model

### 4.2.1 CoolRISC© 816 Architecture

Figure 4.1 shows the CoolRISC© Core 816 architecture which is a 8-bit microprocessor core available with 16 registers and 22-bit wide instructions.

4.2.2 Instruction Set

Table 4.2 presents the instruction set of the CoolRISC© 816.

The CoolRISC© provides a RISC instruction set with four main categories:

- branch instructions

- transfer instructions

- arithmetic and logic instructions

- special instructions.

Unlike most RISC microprocessors, the CoolRISC© core provides instructions that can operate with operands stored either in registers or *in the Data Memory*. All arithmetic and logic instructions can be executed with a first operand in a register and a second operand either in the Data Memory or in a second register. The result can be stored either in a third register or in the first one.

Furthermore, unlike RISC microprocessors and similarly to classic 8-bit microprocessors, the CoolRISC© architecture provides an accumulator (**a**) located at the ALU output. This accumulator stores the last ALU result and should be used as an intermediate result for the next ALU operation. This accumulator is mapped in the register bank.

Similarly, both the Branch & Link instruction of RISC microprocessors (Software Call) and the classic hardware Call are provided by the CoolRISC© architecture.

CoolRISC© architecture can be used from the programming point of view, either as a true RISC architecture or as a more classic 8-bit architecture.

The CoolRISC© 816, with its overflow flag (V) and its arithmetic instructions (SHRA, CMPA, MULA, MSHRA) fully supports signed numbers in the two-complement representation. The MUL & MULA instructions execute a 8 by 8 multiplication. Because the result is on 16 bits, the 8 MSB bits are stored in the destination register and the 8 LSB bits are stored in the accumulator **a**. All the flags (C, Z, V) must be considered as unknown after these instructions.

The multiple shift instructions **MSHL**, **MSHR** & **MSHRA** use the multiplication instructions with an immediate operand. For this reason, the value of **a** is different from the destination register, as in the **MUL** & **MULA** instructions. This implies that the shifted "out" bits are never lost (they are either in **a** or in the destination register), and these instructions can be used to split a byte into two bytes, with a single instruction. For example, a "SWAP r0" can be implemented as follows:

|      |        | i r0 = 0xYZ         |

|------|--------|---------------------|

| MSHL | r0, #4 | ; r0 <- 0Y, a <- Z0 |

| ADD  | r0, a  | ; r0 <- ZY          |

The conditional move instructions (**CMVD** & **CMVS**) can be used to find the maximum (or minimum) value in a table. If **i0** is a pointer to the table, r0 will contain its maximum value after the following sequence:

| CMP(A) r0, (i0) |   |    |     |        |    |      |    |        |

|-----------------|---|----|-----|--------|----|------|----|--------|

| CMVS r0, (i0)+  | ; | r0 | < - | DM(i0) | if | r0   | <  | DM(i0) |

| CMP(A)r0, (i0)  |   |    |     |        |    |      |    |        |

| CMVS r0, (i0)+  | ; | r0 | < - | DM(i0) | if | r0 < | DI | M(i0)  |

|                 |   |    |     |        |    |      |    |        |

| nation |

|--------|

| inforn |

|        |

| minary |

| NAME   | Parameters     | res   | op1   | op2 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MODIF.             |